ASIC, FPGA & SoC Verification¶

Formal Verification¶

Formal Verification has become an essentially strategy to sign-off of complex ASICs and SoC Designs. For DV engineers with a background in Functional Verification (UVM), getting started on Formal Verification can seem overwhelming and a steep hill to climb.

In these set of articles, we start by building a strong foundation in SystemVerilog Assertions (SVA) -- which is the building blocks of Formal Verification. Then proceed to understand what exactly Formal is and how it can help in the DV effort. Finally, I present a blueprint or a playbook which explains step-by-step how you can use Synopsys' VC Formal tool to perform Formal Verification.

SystemVerilog Assertions Basics

A tutorial on SVA, assertion types, |->, |=>, cover property, with tons of examples

A Gentle Introduction to Formal Verification

What is Formal, When to use Formal, Formal vs Functional Verification

A Blueprint for Formal Verification

Get your hands dirty with your first FV testbench. Also includes a path to signing off with Formal.

SystemVerilog Language & UVM¶

This collection of articles attempts to be the best explanation of concepts in SystemVerilog, UVM (Universal Verification Methodology) and any other concepts related to DV (Design Verification).

It is dense with working code examples, which can also be used as a quick reference.

SystemVerilog Generate Construct

A detailed look at how to use generate in loops, conditions and assertions

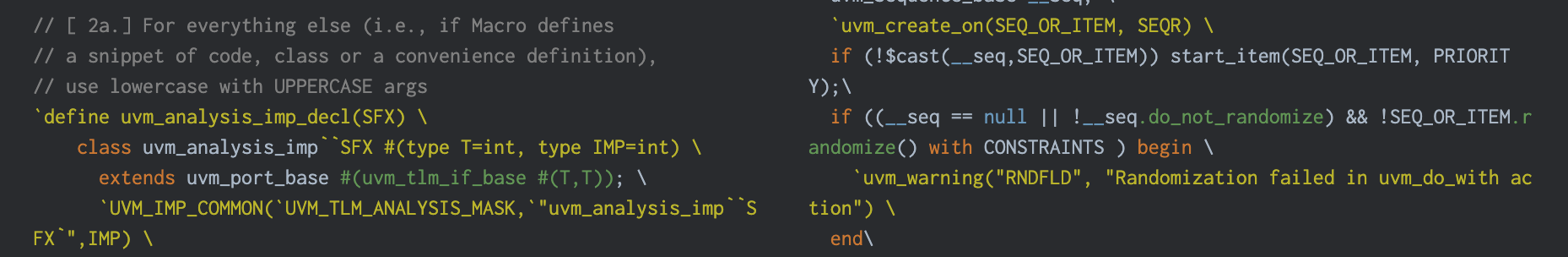

SystemVerilog Macros

In-depth tutorial of how to write macros, what do those , `` &" mean

SystemVerilog Randomization & Random Number Generation

$random, $urandom, $urandom_range, randomize, std::randomize

SystemVerilog Random Stability

Deep dive into Random Stability, Rand State and how to recreat failed tests

Style Guide for SystemVerilog Code

Inspired by Python PEP8, this is the missing Styleguide for SystemVerilog. Make code beautiful again.

10 Useful SystemVerilog Utilities

__FILE__, __LINE__, $countbits, $size and more ...

How to Create & Use VMC SWIFT Models

How to securely distribute IP simulation models